About Me

Physical Design Verification Engineer at TSMC with an M.S. in Electrical and Computer Engineering from UCLA. Experienced in advanced process CPU physical design and RTL implementation across 4nm, 3nm, and 2nm technology nodes. Skilled in LVS, DRC, ECO, timing closure, congestion analysis, and power optimization using Cadence Innovus and related EDA tools. Strong foundation in VLSI design, computer architecture, and semiconductor fabrication processes. Focused on delivering reliable, high-performance solutions for complex chip designs under aggressive schedules.

Professional Experience

-

TSMC - Taiwan Semiconductor Manufacturing Company Limited

Sep. 2024 – Present | Full-time Onsite PositionCPU Physical Design Verification Engineer | USA

• Managed a diverse project portfolio with direct contributions to physical verification tasks such as LVS, Metal DRC, Base DRC, ANT cleanup, RLMB fixing, and functional ECOs, including developing TCL scripts to efficiently resolve Metal DRC violations.

• Ran the physical design flow, while using Cadence Innovus interactively to perform shielding for critical nets to ensure timing closure and congestion analysis to prevent unerasable Metal DRCs in the final stage.

• Helped tape out multiple high-performance CPU projects across 4nm, 3nm, and 2nm process nodes, contributing to achieving timing closure and improving routing congestion for final layouts.

• Collaborated with global, cross-functional teams to resolve complex design and verification challenges, ensuring on-time delivery of high-quality silicon. -

A*STAR - Agency for Science, Technology and Research

Jun. 2023 – Sep. 2023 | Full-time Onsite PositionIntegrated Circuit Design & System (ICDS) Research Assistant

• Enhanced keyword spotting (KWS) detection accuracy by 10.3% through LSTM cell implementation in Python

• Conducted comprehensive analysis of quantization effects on model accuracy using .npz data analysis

• Optimized Verilog blocks using TSMC 40nm IP, achieving improved accuracy through register bit allocation -

UCLA Henry Samueli School of Engineering and Applied Science

Apr. 2023 – Jun. 2023 | Part-time PositionGraduate Student Reader

• Supported CS136 (Computer Security) course instruction through comprehensive assessment and feedback

Education

-

University of California, Los Angeles

Sep. 2022 – Jun. 2024Master of Science in Electrical and Computer Engineering GPA: 3.72/4.0

-

University of Leeds

Sep. 2018 – Jun. 2022Bachelor of Science in Electronic and Electrical Engineering First Class Honours

-

Southwest Jiaotong University

Sep. 2018 – Jun. 2022Bachelor of Science in Electronic and Electrical Engineering Major GPA: 3.7/4.0

Technical Projects

-

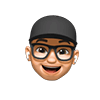

4X4 Multiplier Tapeout | Cadence Virtuoso

Jan. 2023 - Dec. 2023• Designed and implemented a 4x4 multiplier using SkyWater130nm library, featuring resettable static-CMOS register and 28-transistor mirror adder

• Achieved successful DRC, LVS, and PEX verifications with optimized pipeline execution and timing closure

• Developed comprehensive test plan and PCB design, achieving 0.1 GHz operation frequency -

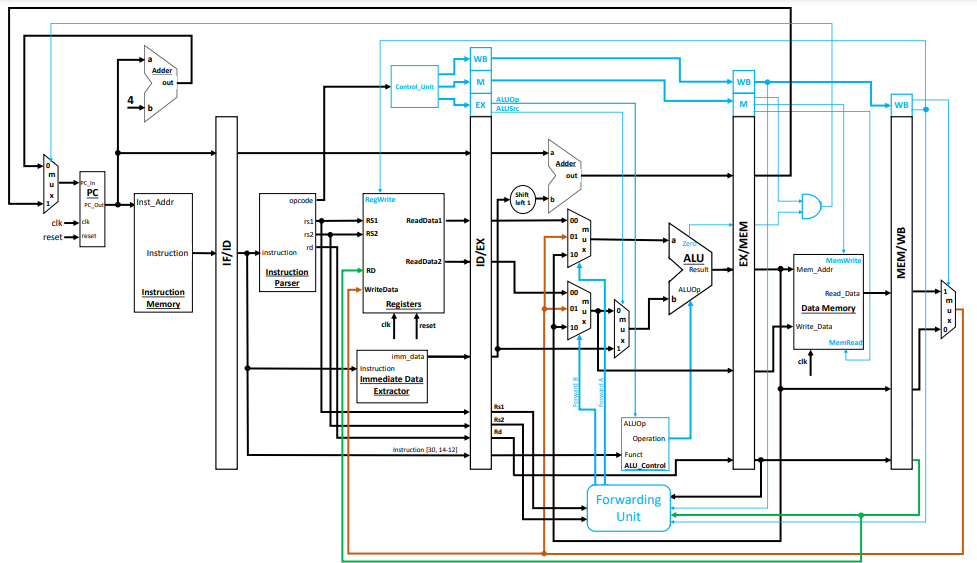

FPGA-based Digital Audio Visualizer | System Verilog, FFT, I2C, VGA

Sep. 2022 - Jun. 2023• Implemented 32-point FFT engine with Low Pass Filtering and dynamic VGA display on Intel-DE10 board

• Developed I2C communication protocol for gyroscope and accelerometer integration

• Project selected for final showcase due to innovative display implementation -

CPU Memory Controller | C++

Nov. 2022 - Dec. 2022• Designed two-level memory hierarchy with direct-mapped L1 and 8-way set-associative L2 cache

• Implemented LRU replacement policy and write-through strategy for optimal performance

• Analyzed and optimized cache performance metrics including miss rate and access time -

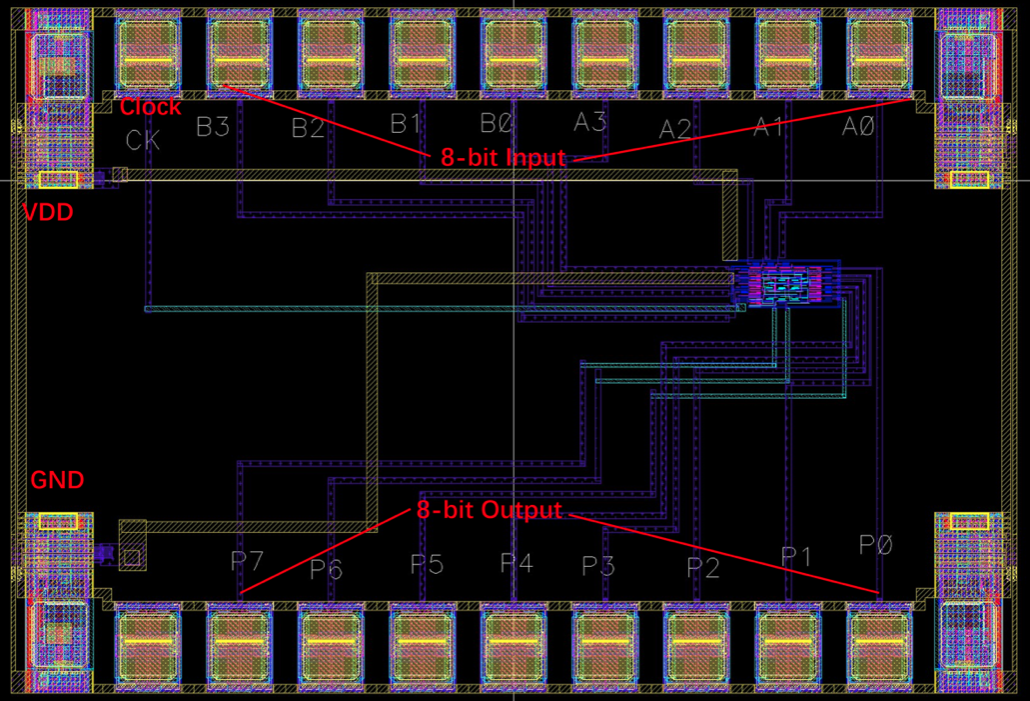

RISC-V Five-Stage Pipeline Core | Verilog, RISC-V

Jan. 2023 - Mar. 2023• Developed RISC-V 5-stage pipeline CPU with comprehensive instruction set support

• Implemented Hazard Detection Unit and pipeline stages with ModelSim verification